微处理器的外部总线接口(External Bus Interface;EBI)用于存取或控制外部的周边装置,但是闪存、同步动态随机存取内存(SDRAM)各自拥有特定的装置接口。原因之一是免费代理软件接口这些类型的内存芯片在存取内部储存单元(storage cell)时所需耗费的时间远远大于EBI的作业时间,另一原因是不同类型的内存有其独特的存取特性。例如,闪存对于储存单元的写入是程序化(programming),在程序化之前必须先抹除(erase)。

SPMI的硬件结构和软件工程

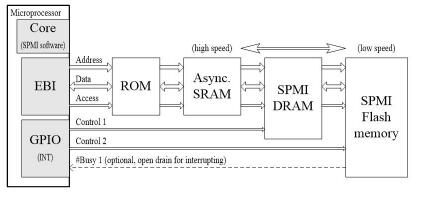

图 1呈现微处理器和各类型的内存之间应用软件代理内存接口(Software Proxy Memory Interface;SPMI)的硬件结构(关于软件代理接口的更多讨论,请参考笔者先前发表的《软件代理接口提升内存存取效率》一文)。软件程序在微处理器内部执行时控制二输出脚,并且协同EBI来存取或控制各种内存。这二输出脚的讯号是单元存取致能(cell access enable,#CAE)以及启动(activating,#ACT),形成如图 1所示的一组控制讯号,亦即‘Control 1’。由于闪存在进行程序化和抹除时皆需耗费非常久的时间,所以使用另一组控制讯号,亦即‘Control 2’。

依据内存的存取特性和访问时间来撰写其所对应的软件程序,软件工程师必须适时使用EBI来传输数据和控制GPIO来操作内存装置。当SPMI的程序代码被微处理器执行时,EBI和GPIO一定是循序动作;其中,EBI负责传输数据,GPIO负责控制储存单元的存取,并且依据内存的存取特性来交替使用EBI和GPIO。这是简单介绍SPMI在软件工程上的基本知识;顺便一提,用于存取DRAM的程序代码也可转成微处理器的微码(microcode)。

SPMI的特征

图 2呈现SPMI DRAM与[DDR-n] SDRAM的差异,用来介绍SPMI的独到特征。SPMI DRAM芯片包含控制逻辑(control logic),但没有自动更新(auto refresh)以及延迟锁定回路(DLL),这样的硬件架构可降低单一芯片的成本。除此之外,SDRAM的控制逻辑比SPMI DRAM更加复杂。软件工程师可善加利用系统单芯片(SoC)的内部装置以及硬件平台的装置来实现自动更新的功能。

对于基本的自动更新,其所相关的硬件电路包含定时器,更进阶的自动更新就需要温度传感器;这一定时器以及温度传感器并不要求精确度也不要求速度。如果在SDRAM芯片内部执行自动更新会产生正比于芯片数量的功率消耗。SoC可以包含高效率处理器和低功率处理器,某些SoC也有温度传感器;除此之外,先进的硬件平台会侦测SoC与周边芯片之间的环境温度。因此,当SoC在低功率运行时,SPMI的软件程序可以使用低频率定时器和各温度传感器来执行自动更新。例如,SoC透过内部的N模计数器来降低核心的工作频率,然后使用图 2所示的第一定时器、核心温度传感器、周边温度传感器。

异步SRAM的访问时间可以直接换算出操作频率的极限或直接判断存取效率的良窳,但DDR-n SDRAM的操作频率受限于DLL的锁定频率(lock in frequency),其存取效率受限于速度箱(speed bin)的数值。DLL的电路设计有其预定的频率范围,于是SDRAM控制器的频率频率不能大幅变更;这对于硬件工程师在设计硬件平台时,不易在应用设计与组件规格之间取得较佳的平衡;当这一硬件平台转给软件工程师之后就成了锱铢必较的软件工程。

软件程序与数字逻辑之间具有互换的本质,于是SPMI的功能可以转换成硬件控制器,此即图 2所示的SPMI控制器。由于SPMI的动作仅是单纯控制EBI和GPIO的时序,所以该控制器的硬件组件可以使用电场可程序门阵列(Field Programmable Gate Array;FPGA),或是复合型可程序逻辑组件(Complex Programmable Logic Device;CPLD)。

(译名解读:原文‘Field’应是暗喻应用经由横向电场而能工作的晶体管,即「场效晶体管」(FET);而原文‘Gate’在开发上应不受限于「逻辑闸」,例如模拟开关也是一种闸;原文‘Complex’在硬件架构上则是复合许多PLD。)

免费代理软件接口实现灵活的内存配置图二

SPMI闪存的操作

闪存的缺点就是储存单元必须先具有初始的储存状态,也就是要先被抹除,然后才能改变储存状态,也就是程序化;在储存单元被改变储存状态后只能再次抹除才能回到初始的储存状态。若储存单元从初始的储存状态至最高的储存状态仅有一个位阶可被变动,这就称为单阶单元(SLC)。若储存单元能有多个位阶,这就称为多阶单元(MLC),但这时的实际产品仅有3个位阶。于是,三重阶单元(Triple-Level Cell;TLC)意指二进制数学式,也就是2的3次方。

固态硬盘(SSD)在起始发展时是使用NAND闪存,为了提高写入速度,因此设定同一储存地址不能被覆写,所以SSD会损失一些用户数据的储存空间来放置查找表;另外在背景作业中进行抹除,也就是垃圾收集(garbage collection)。在硬件平台上的SPI Flash也多是NAND闪存,所以本文以NAND闪存的存取特性来呈现SPMI的操作时序。

NAND闪存在执行抹除时的单位是区块(block),在执行程序化时的单位是页(page),对应其硬件架构而定义EBI的地址线以及数据线如下:全部地址线在首次数据搬移指令执行时分别是软件芯片寻址(software chip addressing,A[MSB:r])、列地址(A[r-1:0]),其中,列地址包含区块地址和页地址;在首次数据搬移指令执行后,列地址变成行地址。全部数据线在首次数据搬移指令执行时分别是库地址(DQ[7:4])、功能编号(DQ[3:0]),其中,库地址包含逻辑单位编号(logical unit number; LUN)和平面编号(plane number);在首次数据搬移指令执行后是数据。SPMI NAND闪存的指令真值表如下。

免费代理软件接口实现灵活的内存配置图三

读取时序

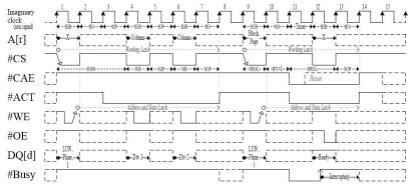

图 3呈现SPMI NAND闪存在读取期间的时序,其中,tEBI代表EBI的访问时间,tIO代表输出埠的控制时间,tOP代表脚本的操作时间,Timer代表定时器的时间。虚构频率(imaginary clock)是用来代表不同时间点的数据传输时间。第1虚构频率至第2虚构频率是执行功能编号‘4’。在第3虚构频率到达之后,#CAE以及#ACT的逻辑讯号转成低准位,然后启动低频率定时器。这一时间点是侦测储存单元的储存状态,然后写入芯片内部的数据缓存器。

微处理器在第4虚构频率确认芯片是否仍在忙碌状态(busy status);如果读取到的数据是‘0x0F’,这表示数据缓存器已完成记录储存单元的储存状态,并且芯片处于备妥状态(ready status)。微处理器在第5虚构频率指令#CAE以及#ACT的逻辑讯号转成高准位。当#ACT的逻辑讯号再次回到高准位之时内存芯片的工作状态立即解除。

第7虚构频率至第12虚构频率是执行功能编号‘0’,微处理器会随机读取芯片内部的数据缓存器。当#ACT的逻辑讯号再次回到高准位之时内存芯片的工作状态立即解除。

写入时序

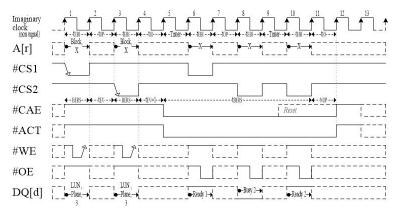

图 4呈现SPMI NAND闪存在写入期间的时序。第1虚构频率至第7虚构频率是是执行功能编号‘1’,微处理器的数据会随机写入芯片内部的数据缓存器,所以不必改变#CAE的逻辑准位;在#ACT的逻辑讯号转成低准位之后,内存芯片才会执行后续的操作步骤。当#ACT的逻辑讯号再次回到高准位之时内存芯片的工作状态立即解除。

第9虚构频率至第11虚构频率是执行功能编号‘5’,也就是对储存单元进行程序化。闪存在接收到程序化指令(PROG)之后启动程序化电压产生器,从启动至稳定的时间(tPV)至少占用1个tIO。微处理器在第10虚构频率指令#CAE以及#ACT的逻辑讯号转成低准位。

微处理器在第11虚构频率启动低频率定时器。第12虚构频率,微处理器确认芯片是否仍在忙碌状态;如果读取到的数据是‘0x0F’,那就表示储存单元已完成程序化,并且芯片处于备妥状态。微处理器在第13虚构频率指令#CAE以及#ACT的逻辑讯号转成高准位。当#ACT的逻辑讯号再次回到高准位之时内存芯片的工作状态立即解除。

免费代理软件接口实现灵活的内存配置图四

抹除时序

图 5呈现SPMI NAND闪存在抹除期间的时序,以下说明如何对多个闪存芯片同时进行抹除。第1虚构频率至第2虚构频率是对某一芯片执行功能编号‘3’,也就是对某一区块进行抹除。闪存在接收到区块抹除指令(BERS)之后启动抹除电压产生器。第3虚构频率至第4虚构频率是对另一芯片执行功能编号‘3’;软件程序在致能最后的芯片时,抹除电压产生器从启动至稳定的时间(tEV)至少占用1个tIO。微处理器在第4虚构频率指令#CAE以及#ACT的逻辑讯号转成低准位。

微处理器在第5虚构频率启动低频率定时器;在计时结束后,微处理器逐一读取各芯片的状态,并且剔除那些已经处于备妥状态的芯片;以上的动作即是图中所示的第6虚构频率至第10虚构频率。例如,微处理器在第8虚构频率确认第二芯片仍然处于忙碌状态,所以读取到的数据是‘0x00’;紧接着,再次启动低频率定时器;第10虚构频率,微处理器直接读取第二芯片的状态。微处理器在第11虚构频率指令#CAE以及#ACT的逻辑讯号转成高准位。当#ACT的逻辑讯号再次回到高准位之时内存芯片的工作状态立即解除。

免费代理软件接口实现灵活的内存配置图五

结语

SPMI的时序可以在操作过程中透过EBI来读取闪存的忙碌状态,但不能立即得知。闪存芯片包含一接脚,用于向微处理器表示它的忙碌状态,所以微处理器可以透过硬件中断来实时得知芯片是否处于备妥状态。

单核心微处理器在存取相对低速的内存芯片时,无论是透过硬件控制器或是软件程序皆要等待储存单元的储存状态被写入电路改变或被读取电路侦测;在这样的条件下并不必担心软件程序会影响应用程序的执行速度。对于多核心微处理器,单一硬件控制器需要预先设定缓冲空间来编排来自各核心的指令,然而软件程序可以灵活配置。

小编介绍的免费代理软件接口实现灵活的内存配置各位看懂了吗?